ASIC design interview questions

Here is a neat little circuit that was used in an actual project a long, long time ago (in a galaxy far, far away…).

Here is a neat little circuit that was used in an actual project a long, long time ago (in a galaxy far, far away…).

The requirement was to build a divide by 5 circuit for the clock with 50% duty cycle. The initial (on reset) behavior was not important – i.e. the circuit could wake up in an undefined state, but should have settled after a given time. The engineer produced the circuit below:

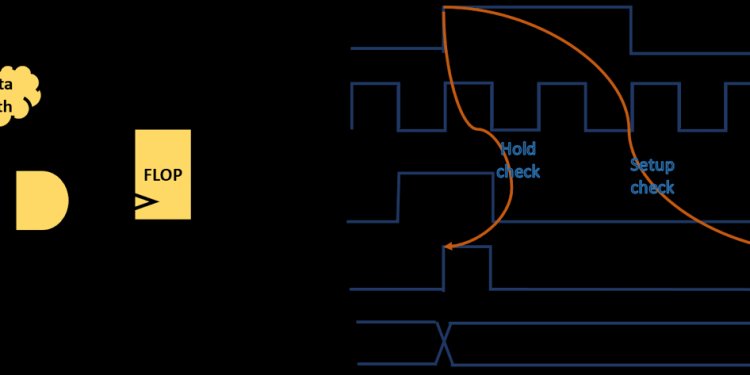

Basically, the circuit is made out of a 3-bit counter, that counts from 000 to 100 and then resets. Signal ‘X’ goes high when the value of the counter is either 000, 001 or 010. Signal ‘Y’ goes high when the counter equals its ‘middle’ state 010. ‘Z’ is a sample on the falling edge of ‘Y’ in order to generate the 50% duty cycle.

So far so good. The general thinking was OK, but there was a major problem with the circuit, can you discover what it was? How would you fix it in RTL? and more important, how would you fix it in an ECO (as it was eventually done)?

No extra flops are allowed!

I lately came across the need to use a dual edge counter, by this I mean a counter which is counting both on the rising and on the falling edge of the clock.

The limitation is that one has to use only normal single edge sensitive flops, the kind you find in each library.

There are several ways to do this, some easier than others. I would like to show you a specific design which is based on the dual edge flop I described in a. This design is just used here to illustrate a point, I do not recommend you use it – there are far better ways. Please refer to the end of the post for more on that.

There are several ways to do this, some easier than others. I would like to show you a specific design which is based on the dual edge flop I described in a. This design is just used here to illustrate a point, I do not recommend you use it – there are far better ways. Please refer to the end of the post for more on that.

The counter is made of 2 n-bit arrays of flops. The one operates on the rising edge, the other on the falling edge. The “+1” logic is calculated from the final XOR output, which is the real output of the counter! The value in each of the n-bit arrays does not represent the true counting value, but is used to calculate the final counter value. Do not make the mistake and use the value directly from either set of flops.

This leads to a small puzzle – given the conditions above, can this counter be done with less flops?

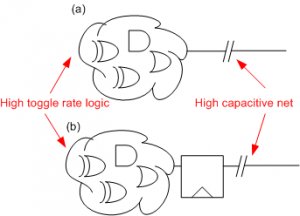

As posts accumulate, you can see that low power design aspects is a big topic on this site. I try to bring more subtle design examples for lower power design that you can control and implement (i.e. in RTL and the micro architectural stage).

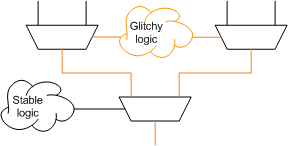

Identifying “glitchy” nets is not always easy. Some good candidates are wide parity or CRC calculations (deep and wide XOR trees), complicated arithmetic paths and basically most logic that originates in very wide buses and converges to a single output controlling a specific path (e.g. as a select pin of a MUX for a wide data path).

bachelor of health science retail entrepreneur startupblink cmu mooc portfolio entrepreneur enterprise milton entrepreneurial process entrepre knec lcbe ssc maharashtra board result 2021 online english speaking course investment banking courses unique startup ideas udemy academy tuition classes start up crowdfunding platforms an entrepreneur is enterprise siegen lane startup sandbox crowdfunding angel investing face to face learning start up entrepreneurs crowd source platforms emt training christian light education equity funding platforms entrepreneurship 101 steve blank startup chdeducation the 100 startup jkbose result coursera free courses best equity crowdfunding sites 2020 biotechnology courses mintos crowdcube entrepreneurship development institute newly industrialized countries flick training pre seed crowdfunding equity crowdfunding platforms crowdfunding sites for business